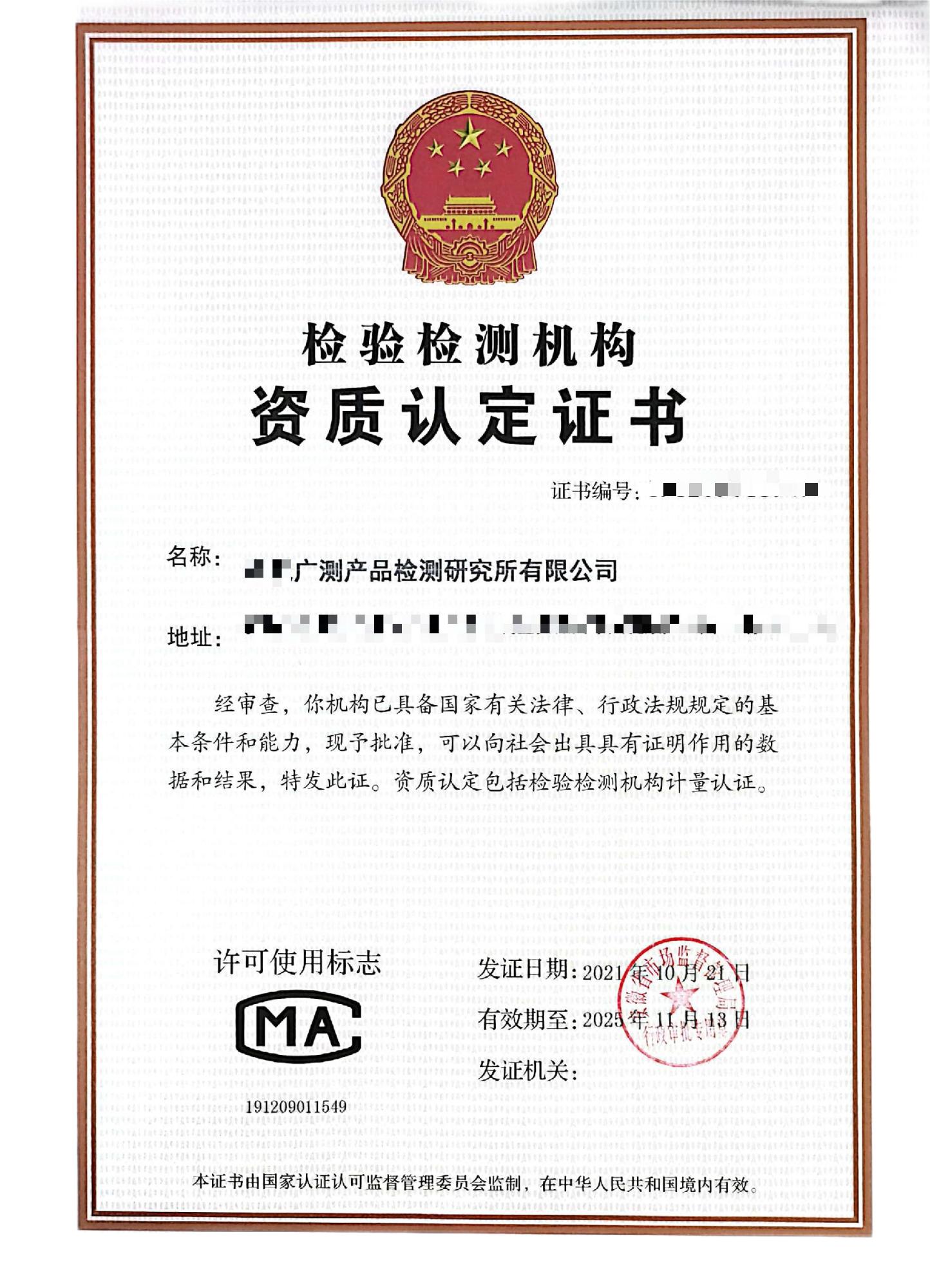

芯片静电防护能力ESD测试是半导体产品先期质量验证的重要关键指针,广测检测已通过资质认可,体系认证。可为您提供芯片防静电能力测试,测试数据准确可靠,实验室信息管理系统,保障每个服务环节的高效、保密运转。

业务挑战

为什么芯片需要防静电

静电是环境中的自然现象,是电荷在物体中的不平衡分布的一种现象。物体带电后,电荷会保持在物体上,故称为静电。静电积累之后,当物体电位不同,电荷通过瞬间电流发生转移的过程即为放电。

半导体产品具有非常细小的线路,为了避免芯片在生产或使用过程中被静电放电所损伤,在集成电路内皆有制作静电放电防护电路。随着半导体产业先进制程发展推进,芯片尺寸不断缩小,ESD耐压能力是否同步提升,在静电防护的能力上也备受挑战,ESD测试是半导体产品先期质量验证的重要关键指针。

芯片防静电能力测试

▶ 芯片放电模拟测试

━ 模拟因人体在地上走动磨擦或其他因素,在人体上已累积了静电,当此人去碰触到芯片时,人体上的静电便会经由芯片的pin脚进入芯片内,再经由芯片放电到地去,瞬间产生的电流可能造成芯片的损毁。

━ 模拟机器设备本身累积了静电,当此机器去碰触到芯片时,该静电便经由芯片的pin脚放电。因机械等效电阻为0奥姆,因此瞬间产生的电流更大,对芯片的破坏力也强。

━ 芯片先因磨擦或其他因素而在内部累积了静电,但在静电累积的过程中并未被损伤。当此带有静电的芯片在使用时,其pin脚碰触到接地面时,芯片内部的静电便会经由pin脚自芯片内部流出来,而造成了放电的现象。

━ 瞬间电流被锁定或者放大,而造成芯片在电源与对地之间造成短路,而因为大电流损伤芯片。由于目前半导体电路设计密度越来越高,电压或电流的瞬间变化对于芯片的损伤也越趋严重。

适用测试标准 : 协助客户通过JEDEC、MIL—STD、AEC-Q等可靠性国际试验标准。

适用产品范围: 集成电路芯片、晶体管、MOS管…等。

常规样品要求: 以具体标准为准。

▶ 检测项目

━ 人体静电测试 (HBM,Human Body Model)

━ 机械静电测试 (MM,Machine Model)

━ 充电放电测试 (CDM,Charged Device Model)

━ 闩锁效应(Latch-up)

━ 传输线脉冲(TLP,Transmission Line Pulse)

▶ 解决方案

━ 1.ESD实验设计

━ 2.ESD测试

━ 3.数据分析与汇整报告

━ 4.ESD培训及咨询

首页

首页

行业检测

行业检测

服务项目

服务项目

咨询报价

咨询报价